# ANALOG 4-Channel, Software Selectable True bipolar DEVICES Input 12 Bit Dive Size 450

**Preliminary Technical Data**

AD7324\*

#### **FEATURES**

- 12-Bit plus Sign SAR ADC

- True Bipolar Input Ranges

- Software Selectable Input Ranges ± 10V, ± 5V, ± 2.5V, 0 to 10V

- 1 MSPS Throughput Rate

- Four Analog Input Channels with Channel Sequencer

- Single Ended, True Differential and Pseudo Differential **Analog Input Capability**

- High Analog Input Impedance

- Low Power:- 12 mW

- Full Power Signal Bandwidth: 7 MHz

- Internal 2.5 V Reference

- High Speed Serial Interface

- Power Down Modes

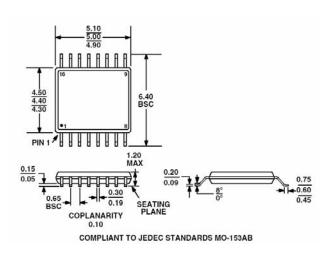

- 16-Lead TSSOP package

- iCMOS™ Process Technology

- · For eight and two channel equivalent devices see AD7328 and AD7322 respectively.

#### **GENERAL DESCRIPTION**

The AD7324 is a 4-Channel, 12-Bit plus Sign Successive Approximation ADC. The ADC has a high speed serial interface that can operate at throughput rates up to 1 Msps.

The AD7324 can accept true bipolar Analog Input signals. The AD7324 has four software selectable inputs Ranges, ±10V, ±5V, ±2.5V and 0 to 10V. Each analog input channel can be independently programmed to one of the four input ranges.

The Analog input channels on the AD7324 can be programmed to be Single-Ended, true Differential or Pseudo Differential.

The AD7324 contains a 2.5V Internal reference. The AD7324 also allows for external Reference operation. If a 3V reference is applied the REF  $_{\mbox{\scriptsize IN/OUT}}$  pin the AD7324 can accept a true Bipolar  $\pm 12V$  Analog Input. Minimum  $V_{DD}$  and  $V_{SS}$  supplies of  $\pm 12V$  are required for the ±12V Input Range.

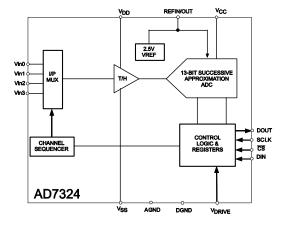

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

#### **PRODUCT HIGHLIGHTS**

- 1. The AD7324 can accept True Bipolar Analog Input signals,  $\pm 10V$ ,  $\pm 5V$ ,  $\pm 2.5V$  and 0 to 10V unipolar signals.

- 2. The Four Analog Inputs can be configured as 4 Single-Ended inputs, 2 True Differential, 2 Pseudo Differential or 3 Pseudo Differential Inputs. The AD7324 has high Impedance Analog Inputs.

- 3. The AD7324 features a High Speed Serial Interface. Throughput Rates up to 1 MSPS can be achieved on the AD7324.

- 4. Low Power, 26 mW at maximum throughput rate of 1 MSPS.

| Device Number | Number of Bits    | Number of Channels |  |  |  |  |

|---------------|-------------------|--------------------|--|--|--|--|

| AD7328        | 12-Bits Plus Sign | 8                  |  |  |  |  |

| AD7322        | 12-Bits Plus Sign | 2                  |  |  |  |  |

*i*CMOS™ Process Technology

For analog systems designers within industrial/instrumentation equipment OEMs who need high performance ICs at higher-voltage levels, iCMOS is a technology platform that enables the development of analog ICs capable of 30V and operating at +/- 15V supplies while allowing dramatic reductions in power consumption and package size, and increased AC and DC performance.

#### Rev. Pri

<sup>\*</sup> Protected by U.S. Patent No. 6,731,232

# **AD7324**

# **Preliminary Technical Data**

# **TABLE OF CONTENTS**

| AD7324—Specifications        | Theory of Operation | 9  |

|------------------------------|---------------------|----|

| Absolute Maximum Ratings     | , .                 |    |

| Pin Functional Descriptions7 | Serial interface    | 20 |

| Terminology                  | OUTLINE DIMENSIONS  | 21 |

#### **REVISION HISTORY**

Revision PrI: Preliminary Version

# AD7324—SPECIFICATIONS<sup>1</sup>

Table 1. Unless otherwise noted,  $V_{DD} = +$  12V to +16.5V,  $V_{SS} = -$ 12V to -16.5V,  $V_{CC} = 2.7$ V to 5.25V,  $V_{DRIVE} = 2.7$ V to 5.25V,  $V_{REF} = 2.5$ V Internal/External,  $f_{SCLK} = 20$  MHz,  $f_{S} = 1$  MSPS  $T_{A} = T_{MAX}$  to  $T_{MIN}$

| Parameter                                                  | Specification   | Units              | Test Conditions/Comments                                                                                                                                                           |

|------------------------------------------------------------|-----------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE                                        |                 |                    | F <sub>IN</sub> = 50 kHz Sine Wave                                                                                                                                                 |

| Signal to Noise Ratio (SNR) <sup>2</sup>                   | 76              | dB min             | Differential Mode                                                                                                                                                                  |

| _                                                          | 72              | dB min             | Single-Ended /Pseudo Differential Mode                                                                                                                                             |

| Signal to Noise + Distortion (SINAD) <sup>2</sup>          | 75              | dB min             | Differential Mode                                                                                                                                                                  |

| -                                                          | 71.5            | dB min             | Single-Ended/Pseudo Differential Mode                                                                                                                                              |

| Total Harmonic Distortion (THD) <sup>2</sup>               | -80             | dB max             |                                                                                                                                                                                    |

| Peak Harmonic or Spurious Noise                            |                 |                    |                                                                                                                                                                                    |

| (SFDR) <sup>2</sup>                                        | -80             | dB max             |                                                                                                                                                                                    |

| Intermodulation Distortion (IMD) <sup>2</sup>              |                 |                    | $F_a = 40.1 \text{ kHz}, F_b = 41.5 \text{ kHz}$                                                                                                                                   |

| Second Order Terms                                         | -88             | dB typ             |                                                                                                                                                                                    |

| Third Order Terms                                          | -88             | dB typ             |                                                                                                                                                                                    |

| Aperature Delay <sup>2</sup>                               | 10              | ns max             |                                                                                                                                                                                    |

| Aperature Jitter <sup>2</sup>                              | 50              | ps typ             |                                                                                                                                                                                    |

| Common Mode Rejection (CMRR) <sup>2</sup>                  | TBD             | dB typ             |                                                                                                                                                                                    |

| Channel-to-Channel Isolation <sup>2</sup>                  | -80             | dB typ             | $F_{IN} = 400 \text{ kHz}$                                                                                                                                                         |

| Full Power Bandwidth <sup>2</sup>                          | 7               | MHz typ            | @ 3 dB                                                                                                                                                                             |

|                                                            | 1.5             | MHz typ            | @ 0.1 dB                                                                                                                                                                           |

| DC ACCURACY                                                |                 | 71                 | -                                                                                                                                                                                  |

| Resolution                                                 | 12+Sign         | Bits               |                                                                                                                                                                                    |

| Integral Nonlinearity <sup>2</sup>                         | ±1.5            | LSB max            |                                                                                                                                                                                    |

| Differential Nonlinearity <sup>2</sup>                     | ± 0.95          | LSB max            | Guaranteed No Missing Codes to 13-Bits                                                                                                                                             |

| Offset Error <sup>3</sup>                                  | ±8              | LSB max            | Unipolar Range with Straight Binary output coding                                                                                                                                  |

| Offset Error Match <sup>2</sup>                            | ±0.5            | LSB max            | ompoint name with straight smary output country                                                                                                                                    |

| Gain Error <sup>2</sup>                                    | ±6              | LSB max            |                                                                                                                                                                                    |

| Gain Error Match <sup>2</sup>                              | ±0.6            | LSB max            |                                                                                                                                                                                    |

| Positive Full-Scale Error <sup>2</sup>                     | ±3              | LSB max            | Bipolar Range with Twos Complement Output Codin                                                                                                                                    |

| Positive Full Scale Error Match <sup>2</sup>               | ±0.6            | LSB max            | bipolar hange with two complement output could                                                                                                                                     |

| Bipolar Zero Error <sup>2</sup>                            | ±8              | LSB max            |                                                                                                                                                                                    |

| Bipolar Zero Error Match <sup>2</sup>                      | ±0.5            | LSB max            |                                                                                                                                                                                    |

| Negative Full Scale Error <sup>2</sup>                     | ±4              | LSB max            |                                                                                                                                                                                    |

| Negative Full Scale Error Match <sup>2</sup>               | ±0.5            | LSB max            |                                                                                                                                                                                    |

| ANALOG INPUT                                               | 20.3            | LSD IIIux          |                                                                                                                                                                                    |

| Input Voltage Ranges                                       | ±10V            | Volts              | $V_{DD} = +10V \text{ min}$ , $V_{SS} = -10V \text{ min}$ , $V_{CC} = 2.7V \text{ to } 5.25V$                                                                                      |

| (Programmed via Range Register)                            | ±5V             | VOICS              | $V_{DD} = +5V \text{ min}, V_{SS} = -5V \text{ min}, V_{CC} = 2.7V \text{ to } 5.25V$<br>$V_{DD} = +5V \text{ min}, V_{SS} = -5V \text{ min}, V_{CC} = 2.7V \text{ to } 5.25V$     |

| (i rogrammed via nange negister)                           | ±2.5V           |                    | $V_{DD} = +5V \text{ min, } V_{SS} = -5V \text{ min, } V_{CC} = 2.7V \text{ to } 5.25V$<br>$V_{DD} = +5V \text{ min, } V_{SS} = -5V \text{ min, } V_{CC} = 2.7V \text{ to } 5.25V$ |

|                                                            | 0 to 10V        |                    | $V_{DD} = +10V \text{ min}, V_{SS} = -3V \text{ min}, V_{CC} = 2.7V \text{ to } 5.25V$<br>$V_{DD} = +10V \text{ min}, V_{SS} = 0 \text{ V min}, V_{CC} = 2.7V \text{ to } 5.25V$   |

|                                                            | 0 10 100        |                    | See Table 5                                                                                                                                                                        |

| DC Leakage Current                                         | ±10             | nA max             | See Table 3                                                                                                                                                                        |

| Input Capacitance                                          | 12              | pF typ             | When in Track, ±10V Range                                                                                                                                                          |

| input capacitance                                          | 15              | pF typ             | When in Track, ±10V hange When in Track, ±5V, 0 to 10V Range                                                                                                                       |

|                                                            | 20              |                    | When in Track, ±5V, 0 to 10V kange  When in Track, ±2.5V Range                                                                                                                     |

|                                                            | 3               | pF typ<br>pF typ   | When in Hold                                                                                                                                                                       |

| REFERENCE INPUT/OUTPUT                                     | J               | рі тур             | when in riola                                                                                                                                                                      |

|                                                            | 12 5 to 131/    | V min to max       |                                                                                                                                                                                    |

| Input DC Loakago Current                                   | +2.5 to +3V     |                    |                                                                                                                                                                                    |

| Input Capactianse                                          | ±1<br>20        | μA max             |                                                                                                                                                                                    |

| Input Capactiance                                          |                 | pF typ<br>Vmin/max |                                                                                                                                                                                    |

| Reference Output Voltage Reference Temperature Coefficient | 2.49/2.51<br>25 |                    | 10 nnm/°C tun                                                                                                                                                                      |

| · · · · · · · · · · · · · · · · · · ·                      |                 | ppm/°C max         | 10 ppm/°C typ                                                                                                                                                                      |

| Reference Output Impedance                                 | 25              | $\Omega$ typ       |                                                                                                                                                                                    |

| Parameter                                       | Specification             | Units     | Test Conditions/Comments                                   |

|-------------------------------------------------|---------------------------|-----------|------------------------------------------------------------|

| LOGIC INPUTS                                    |                           |           |                                                            |

| Input High Voltage, V <sub>INH</sub>            | 2.4                       | V min     |                                                            |

| Input High Voltage, V <sub>INL</sub>            | 0.8                       | V max     | $V_{CC} = 4.75 \text{ to } 5.25 \text{ V}$                 |

| , 3                                             | 0.4                       | V max     | $V_{CC} = 2.7 \text{ to } 3.6 \text{ V}$                   |

| Input Current, I <sub>IN</sub>                  | ± 1                       | μA max    | $V_{IN} = 0V \text{ or } V_{CC}$                           |

| Input Capacitance, C <sub>IN</sub> <sup>3</sup> | 10                        | pF max    |                                                            |

|                                                 |                           | '         |                                                            |

| LOGIC OUTPUTS                                   |                           |           |                                                            |

| Output High Voltage, V <sub>OH</sub>            | V <sub>DRIVE</sub> - 0.2V | V min     | $I_{SOURCE} = 200 \mu\text{A}$                             |

| Output Low Voltage, Vol                         | 0.4                       | V max     | I <sub>SINK</sub> = 200 μA                                 |

| Floating State Leakage Current                  | ±1                        | μA max    |                                                            |

| Floating State Output Capacitance <sup>3</sup>  | 10                        | pF max    |                                                            |

| Output Coding                                   | Straight                  | Pa.x      | Coding bit set to 1 in Control Register                    |

| output county                                   | Natural                   |           | county are set to 1 m. control neglecter                   |

|                                                 | Binary                    |           |                                                            |

|                                                 | Two's                     |           | Coding bit set to 0 in Control Register                    |

|                                                 | Complement                |           |                                                            |

| CONVERSION RATE                                 |                           |           |                                                            |

| Conversion Time                                 | 800                       | ns max    | 16 SCLK Cycles with SCLK = 20 MHz                          |

| Track-and-Hold Acquisition Time                 | 200                       | ns max    | Sine Wave Input                                            |

|                                                 | 200                       | ns max    | Full Scale Step input                                      |

| Throughput Rate                                 | 1                         | MSPS max  | See Serial Interface section                               |

| POWER REQUIREMENTS                              |                           |           | Digital Inputs = 0V or V <sub>CC</sub>                     |

| $V_{DD}^4$                                      | 12V/+16.5V                | V min/max | See Table 5                                                |

| Vss <sup>4</sup>                                | -12V/16.5V                | V min/max | See Table 5                                                |

| Vcc                                             | 2.7V / 5.25V              | V min/max | See Table 5                                                |

| $V_{DRIVE}$                                     | 2.7V/5.25V                | V min/max |                                                            |

| Normal Mode                                     |                           |           |                                                            |

| $I_{DD}$                                        | 300                       | μA max    | $V_{DD} = +16.5V$                                          |

| Iss                                             | 370                       | μA max    | $V_{SS} = -16.5V$                                          |

| lcc                                             | 2                         | mA max    | $V_{CC} = 5.25V$                                           |

| Auto-Standby Mode                               |                           |           | F <sub>SAMPLE</sub> = TBD                                  |

| I <sub>DD</sub>                                 | TBD                       | μA max    |                                                            |

| Iss                                             | TBD                       | μA max    |                                                            |

| lcc                                             | 1.6                       | mA typ    |                                                            |

| Auto-Standby Mode                               |                           |           | $F_{SAMPLE} = TBD$                                         |

| I <sub>DD</sub>                                 | TBD                       | μA max    |                                                            |

| I <sub>SS</sub>                                 | TBD                       | μA max    |                                                            |

| Icc                                             | 1                         | mA typ    |                                                            |

| Full Shutdown Mode                              |                           |           |                                                            |

| $I_{DD}$                                        | 0.9                       | μA max    |                                                            |

| Iss                                             | 0.9                       | μA max    |                                                            |

| Icc                                             | 0.9                       | μA max    | SCLK On or Off                                             |

| POWER DISSIPATION                               |                           |           |                                                            |

| Normal Mode                                     | 26                        | mW max    | $V_{DD} = +16.5V$ , $V_{SS} = -16.5V$ , $V_{CC} = 5.25V$ , |

|                                                 | 12                        | mW typ    | $V_{DD} = +5V$ , $V_{SS} = -5V$ , $V_{CC} = 5V$ ,          |

| Full Shutdown Mode                              | 35                        | μW max    | $V_{DD} = +16.5V$ , $V_{SS} = -16.5V$ , $V_{CC} = 5.25V$ , |

NOTES  $^1$  Temperature ranges as follows: -40°C to +85°C  $^2$  See Terminology  $^3$  Guaranteed by Characterization  $^4$  Functional from  $V_{DD}=+4.75V$  and  $V_{SS}=-4.75V$  Specifications subject to change without notice.

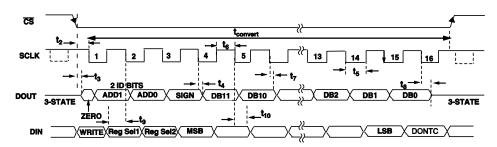

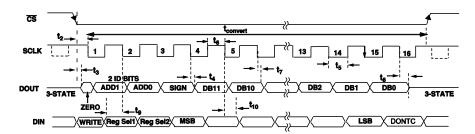

## **TIMING SPECIFICATIONS**

Table 2. Unless otherwise noted,  $V_{DD} = +12V$  to +16.5V,  $V_{SS} = -12V$  to -16.5V,  $V_{CC} = 2.7V$  to 5.25,  $V_{DRIVE} = 2.7V$  to 5.25,  $V_{REF} = 2.5V$  Internal/External,  $T_A = T_{MAX}$  to  $T_{MIN}$

| Parameter             | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit    | Description                                                         |

|-----------------------|----------------------------------------------|---------|---------------------------------------------------------------------|

| f <sub>SCLK</sub>     | 10                                           | kHz min |                                                                     |

|                       | 20                                           | MHz max |                                                                     |

| t <sub>CONVERT</sub>  | 16×t <sub>SCLK</sub>                         | ns max  | $T_{SCLK} = 1/f_{SCLK}$                                             |

| t <sub>QUIET</sub>    | 50                                           | ns max  | Minimum Time between End of Serial Read and Next Falling Edge of CS |

| t <sub>1</sub>        | 10                                           | ns min  | Minimum CS Pulse width                                              |

| t <sub>2</sub>        | 10                                           | ns min  | CS to SCLK Setup Time                                               |

| t <sub>3</sub>        | 20                                           | ns max  | Delay from CS until Dout Three-State Disabled                       |

| t <sub>4</sub>        | TBD                                          | ns max  | Data Access Time after SCLK Falling Edge.                           |

| <b>t</b> <sub>5</sub> | 0.4t <sub>SCLK</sub>                         | ns min  | SCLK Low Pulsewidth                                                 |

| t <sub>6</sub>        | 0.4t <sub>SCLK</sub>                         | ns min  | SCLK High Pulsewidth                                                |

| <b>t</b> <sub>7</sub> | 10                                           | ns min  | SCLK to Data Valid Hold Time                                        |

| t <sub>8</sub>        | 25                                           | ns max  | SCLK Falling Edge to Dout High Impedance                            |

|                       | 10                                           | ns min  | SCLK Falling Edge to Dout High Impedance                            |

| <b>t</b> 9            | TBD                                          | ns min  | DIN set-up time prior to SCLK falling edge                          |

| t <sub>10</sub>       | 5                                            | ns min  | DIN hold time after SCLK falling edge                               |

|                       | 1                                            | μs max  | Power up from Auto Standby                                          |

|                       | TBD                                          | μs max  | Power up from Full Shutdown/Auto Shutdown Mode                      |

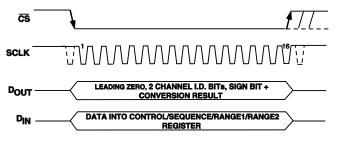

Figure 2. Serial Interface timing Diagram

# **ABSOLUTE MAXIMUM RATINGS**

Table 3.  $T_A = 25^{\circ}C$ , unless otherwise noted

| V <sub>DD</sub> to AGND, DGND                         | -0.3 V to +16.5 V                               |

|-------------------------------------------------------|-------------------------------------------------|

| V <sub>SS</sub> to AGND, DGND                         | +0.3 V to -16.5 V                               |

| V <sub>cc</sub> to AGND, DGND                         | -0.3V to +7V                                    |

| V <sub>DRIVE</sub> to V <sub>CC</sub>                 | $-0.3 \text{ V to V}_{CC} + 0.3 \text{ V}$      |

| AGND to DGND                                          | -0.3 V to +0.3 V                                |

| Analog Input Voltage to AGND                          | V <sub>SS</sub> -0.5V to V <sub>DD</sub> + 0.5V |

| Digital Input Voltage to DGND                         | -0.3 V to +7 V                                  |

| Digital Output Voltage to GND                         | -0.3 V to V <sub>DRIVE</sub> +0.3V              |

| REF <sub>IN</sub> to AGND                             | -0.3 V to V <sub>CC</sub> +0.3V                 |

| Input Current to Any Pin Except Supplies <sup>2</sup> | ±10mA                                           |

| Operating Temperature Range                           | -40°C to +85°C                                  |

| Storage Temperature Range                             | -65°C to +150°C                                 |

| Junction Temperature                                  | +150°C                                          |

| TSSOP Package                                         |                                                 |

| θ <sub>JA</sub> Thermal Impedance                     | 143 °C/W                                        |

| θ <sub>JC</sub> Thermal Impedance                     | 45 °C/W                                         |

| Pb-free Temperature, Soldering                        |                                                 |

| Reflow                                                | 260(+0)°C                                       |

| ESD                                                   | TBD                                             |

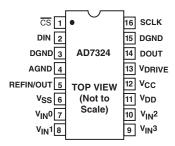

# **Pin Functional Descriptions**

Figure 3. AD7324 Pin Configuration TSSOP

**Table 4. AD7324 Pin Function Descriptions**

| Pin Mnemonic       | Pin Number | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK               | 16         | Serial Clock. Logic Input. A serial clock input provides the SCLK used for accessing the data from the AD7324. This clock is also used as the clock source for the conversion process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| D <sub>оит</sub>   | 14         | Serial Data Output. The conversion output data is supplied to this pin as a serial data stream. The bits are clocked out on the falling edge of the SCLK input and 16 SCLKs are required to access the data. The data stream consists of one leading zero followed by two channel identification bits, followed by the sign bit followed by the 12 bits of conversion data. The data is provided MSB first. See the Serial Interface section.                                                                                                                                                                                                                                                                                                                 |

| CS                 | 1          | Chip Select. Active low logic input. This input provides the dual function of initiating conversions on the AD7324 and frames the serial data transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DIN                | 2          | Data In. Data to be written to the on-chip registers is provided on this input and is clocked into the register on the falling edge of SCLK. See Register section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| AGND               | 4          | Analog Ground. Ground reference point for all analog circuitry on the AD7324. All analog input signals and any external reference signal should be referred to this AGND voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| REF IN/REFOUT      | 5          | Reference Input/ Reference Output pin. The on-chip reference is available on this pin for use external to the AD7324. Alternativley, the internal reference can be disabled and an external reference applied to this input. When using the AD7324 with an external reference, the internal reference must be disabled via the control register. The nominal reference voltage is 2.5 V, which appears at the pin. A 470 nF decoupling capacitor sgould be placed on the Reference pin.                                                                                                                                                                                                                                                                       |

| Vcc                | 12         | Analog Supply Voltage, 2.7 V to 5.25 V. This is the supply voltage for the ADC core on the AD7324. This supply should be decoupled to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $V_{DD}$           | 11         | Positive power supply voltage. This is the positive supply voltage for the Analog Input section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>SS</sub>    | 6          | Negative power supply voltage. This is the negavtive supply voltage for the Analog Input section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>DRIVE</sub> | 13         | The voltage applied to this pin determines the voltage at which the serial interface operates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DGND               | 3,15       | This is the Digital Ground Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Vin0-Vin3          | 7,8,9,10   | Analog input 0 through Analog Input 3. The analog inputs are multiplexed into the on-chip track-and-hold. The analog input channel for conversion is selected by programming the channel address bits, ADD1 through ADD0, in the control register. The inputs can be configured as 4 Single-Ended Inputs, 2 True Differential Input pairs, 2 Pseudo Differential inputs or 3 Pseudo Differential Inputs. The configuration of the Analog inputs is selected by programming the Mode bits, Mode1 and Mode0, in the Control Register. The input range on each input channel is controlled by programming the range register. Input ranges of $\pm 10V$ , $\pm 5V$ , $\pm 2.5V$ and 0 to 10V can be selected on each analog input channel. See Register section. |

## **TERMINOLOGY**

#### **Differential Nonlinearity**

This is the difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

#### **Integral Nonlinearity**

This is the maximum deviation from a straight line passing through the endpoints of the ADC transfer function. The endpoints of the transfer function are zero scale, a point 1 LSB below the first code transition, and full scale, a point 1 LSB above the last code transition.

#### Offset Code Error

This applies to Straight Binary output coding. It is the deviation of the first code transition  $(00 \dots 000)$  to  $(00 \dots 001)$  from the ideal, i.e., AGND + 1 LSB.

#### **Offset Error Match**

This is the difference in Offset Error between any two input channels.

#### **Gain Error**

This applies to Straight Binary output coding. It is the deviation of the last code transition (111 ... 110) to (111 ... 111) from the ideal (i.e.,  $4 \times VRef - 1 LSB$ ,  $2 \times V_{REF} - 1 LSB$ ,  $V_{REF} - 1 LSB$ ) after the offset error has been adjusted out.

#### **Gain Error Match**

This is the difference in Gain Error between any two input channels channels.

#### Bipolar Zero Code Error

This applies when using twos complement output coding and a bipolar Analog Input. It is the deviation of the midscale transition (all 1s to all 0s) from the ideal  $V_{\rm IN}$  voltage, i.e., AGND - 1 LSB

#### **Bipolar Zero Code Error Match**

This refers to the difference in Bipolar Zero Code Error between any two input channels.

#### **Positive Full Scale Error**

This applies when using twos complement output coding and any of the bipolar Analog Input ranges. It is the deviation of the last code transition (011...110) to (011...111) from the ideal ( +4 x  $V_{REF}$  - 1 LSB, + 2 x  $V_{REF}$  - 1 LSB, +  $V_{REF}$  - 1 LSB) after the bipolar Zero Code Error has been adjusted out.

#### Positive Full Scale Error Match

This is the difference in Positive Full Scale error between any two input channels.

#### **Negative Full Scale Error**

This applies when using twos complement output coding and any of the bipolar Analog Input ranges. This is the deviation of the first code transition (10...000) to (10...001) from the ideal

(i.e., - 4 x  $V_{REF}$  + 1 LSB, - 2 x  $V_{REF}$  + 1 LSB, -  $V_{REF}$  + 1 LSB) after the Bipolar Zero Code Error has been adjusted out.

#### **Negative Full Scale Error Match**

This is the difference in Negative Full Scale error between any two input channels.

#### Track-and-Hold Acquisition Time

The track-and-hold amplifier returns into track mode after the fifteenth SCLK falling edge. Track-and-hold acquisition time is the time required for the output of the track-and-hold amplifier to reach its final value, within  $\pm 1/2$  LSB, after the end of conversion.

#### Signal to (Noise + Distortion) Ratio

This is the measured ratio of signal to (noise + distortion) at the output of the A/D converter. The signal is the rms amplitude of the fundamental. Noise is the sum of all non-fundamental signals up to half the sampling frequency ( $f_s/2$ ), excluding dc. The ratio is dependent on the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise. The theoretical signal to (noise + distortion) ratio for an ideal N-bit converter with a sine wave input is given by:

Signal to (Noise + Distortion) =

$$(6.02N + 1.76) dB$$

Thus for a 13-bit converter, this is 80.02 dB.

#### **Total Harmonic Distortion**

Total harmonic distortion (THD) is the ratio of the rms sum of harmonics to the fundamental. For the AD7324 it is defined as:

$$THD(dB) = 20\log \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_1}$$

where  $V_1$  is the rms amplitude of the fundamental and  $V_2$ ,  $V_3$ ,  $V_4$ ,  $V_5$  and  $V_6$  are the rms amplitudes of the second through the sixth harmonics.

#### **Peak Harmonic or Spurious Noise**

Peak harmonic or spurious noise is defined as the ratio of the rms value of the next largest component in the ADC output spectrum (up to fS/2 and excluding dc) to the rms value of the fundamental. Normally, the value of this specification is determined by the largest harmonic in the spectrum, but for ADCs where the harmonics are buried in the noise floor, it will be a noise peak.

#### **Channel-to-Channel Isolation**

Channel-to-channel isolation is a measure of the level of crosstalk between any two channels. It is measured by applying a full-scale, 400 kHz sine wave signal to all unselected input channels and determining how much that signal is attenuated in

the selected channel with a 50 kHz signal. The figure given is the worst-case across all eight channels for the AD7324.

#### **Intermodulation Distortion**

With inputs consisting of sine waves at two frequencies, fa and fb, any active device with non-linearities will create distortion products at sum and difference frequencies of  $mfa \pm nfb$  where m, n = 0, 1, 2, 3, etc. Intermodulation distortion terms are those for which neither m nor n are equal to zero. For example, the second order terms include (fa + fb) and (fa - fb), while the third order terms include (fa + fb), (fa + fb), (fa + fb) and (fa - fb).

The AD7324 is tested using the CCIF standard where two input frequencies near the top end of the input bandwidth are used. In this case, the second order terms are usually distanced in frequency from the original sine waves while the third order terms are usually at a frequency close to the input frequencies. As a result, the second and third order terms are specified separately. The calculation of the intermodulation distortion is as per the THD specification where it is the ratio of the rms sum of the individual distortion products to the rms amplitude of the sum of the fundamentals expressed in dBs.

#### **PSR (Power Supply Rejection)**

Variations in power supply will affect the full-scale transition but not the converter's linearity. Power supply rejection is the maximum change in full-scale transition point due to a change in power supply voltage from the nominal value. See Typical Performance Curves.

#### **Theory of Operation**

#### **CIRCUIT INFORMATION**

The AD7324 is a fast, 4-Channel, 12-Bit Plus Sign, Bipolar Input, Serial A/D converter. The AD7324 can accept bipolar input ranges that include ±10V, ±5V, ±2.5V, it can also accept 0 to 10V unipolar input range. A different Analog input range can be programmed on each analog input Channel via the on-chip range register. The AD7324 has a high speed serial interface that can operate at throughput rates up to 1 MSPS.

The AD7324 requires  $V_{\rm DD}$  and  $V_{\rm SS}$  dual supplies for the high voltage Analog input structure. These supplies must be equal to or greater than the Analog input range. See Table 5 for the minimum requirements on these supplies for each Analog Input Range. The AD7324 requires a low voltage 2.7V to 5.25 V  $V_{\rm CC}$  supply to power the ADC core.

Table 5. Reference and Supply Requirements for each Analog Input Range

| Selected<br>Analog<br>Input<br>Range (V) | Reference<br>Voltage<br>(V) | Full<br>Scale<br>Input<br>Range(V) | AV <sub>CC</sub><br>(V) | Minimum<br>V <sub>DD</sub> /V <sub>SS</sub> (V) |

|------------------------------------------|-----------------------------|------------------------------------|-------------------------|-------------------------------------------------|

| ±10                                      | 2.5                         | ±10                                | 3/5                     | ±10                                             |

| ±10                                      | 3.0                         | ±12                                | 3/5                     | ±12                                             |

| ± 5                                      | 2.5                         | ±5                                 | 3/5                     | ±5                                              |

| <u> </u>                                 | 3.0                         | ±6                                 | 3/5                     | ±6                                              |

| ±2.5                                     | 2.5                         | ±2.5                               | 3/5                     | ±5                                              |

| ±2.5                                     | 3.0                         | ±3                                 | 3/5                     | ±5                                              |

| 0 to 10                                  | 2.5                         | 0 to 10                            | 3/5                     | +10/AGND                                        |

| 0 10 10                                  | 3.0                         | 0 to 12                            | 3/5                     | +12/AGND                                        |

In order to meet the specified performance specifications when the AD7324 is configured with the minimum  $V_{\rm DD}$  and  $V_{\rm SS}$  supplies for a chosen Analog input range the throughput rate should be decreased from the maximum throughput range. See typical performance curves.

The Analog Inputs Can be configured as either 4 Single-Ended inputs, 2 True Differential Inputs, 2 Pseudo Differential Inputs or 3 Pseudo Differential Inputs. Selection can be made by programming the Mode bits, Mode0 and Mode1, in the Control Register.

The serial clock input accesses data from the part but also provides the clock source for each successive approximation ADC. The AD7324 has an on-chip 2.5 V reference. However the AD7324 can also work with an external Reference. On power up the external reference operation is the default option. If the internal Reference is the preferred option the user must write to the reference bit in the control register to select the internal Reference operation.

The AD7324 also features power-down options to allow power saving between conversions. The power-down modes are selected by programming the on-chip Control Register, as described in the Modes of Operation section.

#### **CONVERTER OPERATION**

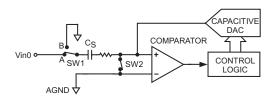

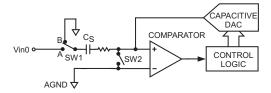

The AD7324 is a successive approximation analog-to-digital converter, based around two capacitive DACs. Figure 4 and Figure 5 show simplified schematics of the ADCs in Single Ended Mode during the acquisition and conversion phase, respectively. Figure 6 and Figure 7 show simplified schematics of the ADCs in Differential Mode during acquisition and conversion phase, respectively. The ADC is comprised of control logic, a SAR, and a capacitive DAC. In Figure 4 (the acquisition phase), SW2 is closed and SW1 is in position A, the comparator is held in a balanced condition, and the sampling capacitor array acquires the signal on the input.

Figure 4. ADC Acquisition Phase(Single Ended)

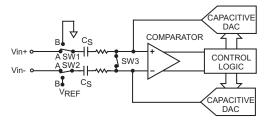

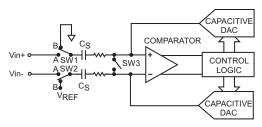

When the ADC starts a conversion (Figure 5), SW2 will open and SW1 will move to position B, causing the comparator to become unbalanced. The control logic and the charge redistribution DAC is used to add and subtract fixed amounts of charge from the sampling capacitor arrays to bring the comparator back into a balanced condition. When the comparator is rebalanced, the conversion is complete. The Control Logic generates the ADC output code

Figure 5. ADC Conversion Phase(Single Ended)

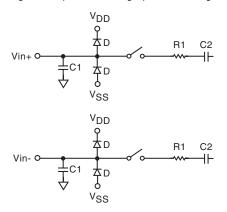

Figure 6 shows the differential configuration during the Acquisition phase. For the Conversion Phase, SW3 will open, SW1 and SW2 will move to position B, see Figure 7. The output impedances of the source driving the Vin+ and Vin- pins must be matched; otherwise the two inputs will have different settling times, resulting in errors.

Figure 6. ADC Differential Configuration during Acquisition Phase

Figure 7. ADC Differential Configuration during Conversion Phase

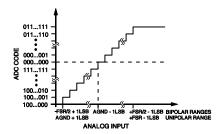

### **Output Coding**

The AD7324 default output coding is set to two's complement. The output coding is controlled by the Coding bit in the Control Register. To change the output coding to Straight Binary Coding the Coding bit in the Control Register must be

set. When operating in Sequence mode the output coding for each channel in the sequence will be the value written to the coding bit during the last write to the Control Register.

#### **Transfer Functions**

The designed code transitions occur at successive integer LSB values (i.e., 1 LSB, 2 LSB, and so on). The LSB size is dependant on the Analog input Range selected.

Table 6. LSB sizes for each Analog Input Range

| Input Range | Full Scale Range/8192 | LSB Size |

|-------------|-----------------------|----------|

| ±10V        | 20V/8192              | 2.441 mV |

| ±5V         | 10V/8192              | 1.22 mV  |

| ±2.5V       | 5V/8192               | 0.61 mV  |

| 0 to 10V    | 10V/8192              | 1.22 mV  |

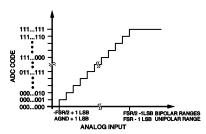

The ideal transfer characteristic for the AD7324 when Twos Complement coding is selected is shown in Figure 8, and the ideal transfer characteristic for the AD7324 when Straight Binary coding is selected is shown in Figure 9.

Figure 8 Twos Complement Transfer Characteristic (Bipolar Ranges)

Figure 9. Straight Binary Transfer Characteristic (Bipolar Ranges)

#### **ANALOG INPUT**

The analog inputs of the AD7324 may be configured as Single-Ended, True differential or Pseudo Differential via the Control Register Mode Bits as shown Table 9 of the Register Section. The AD7324 can accept True bipolar input signals. On power up the Analog inputs will operate as 4 Single-Ended Analog Input Channels. If True Differential or Pseudo Differential is required, a write to the Control register is necessary to change this configuration after power up.

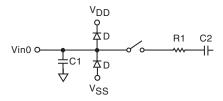

Figure 10 shows the equivalent Analog input circuit of the AD7324 in Single-Ended Mode. Figure 11 shows the equivalent Analog input structure in Differential mode. The Two Diodes provide ESD protection for the Analog Inputs.

Figure 10. Equivalent Analog Input Circuit-(Single Ended)

Figure 11. Equivalent Analog Input Circuit-(Differential)

Care should be taken to ensure the Analog Input never exceeds the  $V_{\rm DD}$  and  $V_{\rm SS}$  supply rails by more than 300 mV. This will cause the diodes to become forward biased and start conducting into either the  $V_{\rm DD}$  or  $V_{\rm SS}$  rails. These diodes can conduct up to 10 mA without causing irreversible damage to the part.

The Capacitor C1, in Figure 10 and Figure 11 is typically 4 pF and can primarily be attributed to pin capacitance. The resistor R1, is a lumped component made up of the on-resistance of the input multiplexer and the track-and-hold switch. The Capacitor C2, is the sampling capacitor, its capacitance will vary depending on the Analog input range selected.

#### **Track-and-Hold Section**

The Track-and-Hold on the Analog Input of the AD7324 allows the ADC to accurately convert an input sine wave of full scale amplitude to 12-Bit Plus Sign accuracy. The input bandwidth of the Track-and-Hold is greater than the Nyquist rate of the ADC, the AD7324 can handle frequencies up to 7 MHz.

The Track-and-Hold enters its tracking mode on the  $15^{th}$  SCLK falling edge after the  $\overline{\text{CS}}$  falling edge. The time required to acquire an input signal will depend on how quickly the sampling capacitor is charged. With zero source impedance 200 ns will be sufficient to acquire the signal to the 13-Bit level.

The acquisition time required is calculated using the following

formula:

$$t_{ACQ} = 10 x ((R_{SOURCE} + R) C)$$

where C is the Sampling Capacitance and R is the resistance seen by the track-and-hold amplifier looking back on the input. For the AD7324, the value of R will include the on-resistance of the input multiplexer. The value of R is typically 300  $\Omega.\ R_{SOURCE}$  should include any extra source impedance on the Analog input.

The AD7324 enters track on the fifteenth SCLK falling edge. When running the AD7324 at a throughput rate of 1 MSPS with a 20 MHz SCLK signal the ADC will have approx. 1 SCLK period plus  $t_8$  plus the quiet time,  $T_{QUIET}$ , in order to acquire the analog input signal. The ADC goes back into hold on the  $\overline{\text{CS}}$  falling edge.

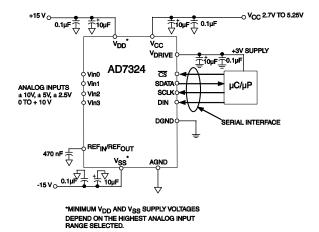

#### TYPICAL CONNECTION DIAGRAM

Figure 12 shows a typical connection diagram for the AD7324. In this configuration the AGND pin is connected to the Analog ground plane of the system. The DGND pin is connected to the Digital ground plane of the system. The Analog Inputs on the AD7324 can be configured to operate in Single Ended, True Differential or Pseudo Differential Mode. The AD7324 can operate with either the internal or an external reference. In Figure 12, the AD7324 is configured to operate with the internal 2.5V reference. A 470 nF decoupling capacitor is required when operating with the internal reference.

The  $V_{\rm CC}$  pin can be connected to either a 3V or a 5V supply voltage. The  $V_{\rm DD}$  and  $V_{\rm SS}$  are the dual supplies for the high voltage analog input structures. The voltage on these pins must be equal to or greater than the highest analog input range selected on the analog input channels, see Table 5 for more information. The  $V_{\rm DRIVE}$  pin is connected to the supply voltage of the microprocessor. The voltage applied to the  $V_{\rm DRIVE}$  input controls the voltage of the serial interface.

Figure 12. Typical Connection Diagram

## **AD7324 REGISTERS**

The AD7324 has three-programmable registers, the **Control Register**, **Sequence Register**, and the **Range Register**. These registers are write only registers.

#### **Addressing these Registers**

A serial transfer on the AD7324 consists of 16 SCLK cycles. The three MSBs on the DIN line during this 16 SCLK transfer are decoded to determine which register is addressed during the serial transfer. The three MSBs consists of the Write bit, Register Select 1 bit and Register Select 2 bit. The Register Select bits are used to determine which of the four on-board registers is selected. The Write bit will determine if the Data on the DIN line following the Register select bits will be loaded into the addressed register or not. If the Write bit is 1 the bits will be loaded into the register addressed by the Register Select bits. If the Write Bit is a 0 the data on the DIN will not be loaded into any register.

Table 7. Decoding Register Select bits and Write bit.

| Write | Register Select1 | Register Select2 | Comment                                                                                                          |

|-------|------------------|------------------|------------------------------------------------------------------------------------------------------------------|

| 0     | 0                | 0                | Data on the DIN line during this serial transfer will be ignored                                                 |

| 1     | 0                | 0                | This combination selects the Control Register. The subsequent 12 bits will be loaded into the Control Register.  |

| 1     | 0                | 1                | This combination selects the Range Register. The subsequent 8 bits will be loaded into the Range Register.       |

| 1     | 1                | 1                | This combination selects the Sequence Register. The subsequent 8 bits will be loaded into the Sequence Register. |

#### CONTROL REGISTER

The Control Register is used to select the Analog Input configuration, Reference, Coding, Power mode etc. The Control Register is a write only 12-bit register. Data loaded on the DIN line corresponds to the AD7324 configuration for the next conversion. Data should be loaded into the Control Register after the Range Register and the Sequence Register has been initialized, that is if the Sequence register is being used. The bit functions of the Control Register are outlined in Table 8.

#### Control Register (The Power-up status of all bits is 0)

Table 8. Control Register

MSB LSB

| Write | Register<br>Select 1 | Register<br>Select 2 | DONTC | ADD1 | ADD0 | Mode1 | Mode0 | PM1 | PM0 | Coding | Ref | Seq1 | Seq2 | ZERO | 0 |

|-------|----------------------|----------------------|-------|------|------|-------|-------|-----|-----|--------|-----|------|------|------|---|

| Bit   | Mnemonic        | Comment                                                                                                                                                                                                                                                                                                                                      |

|-------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12    | DONTC           | Don't Care. The value written to this bit of the Control Register is a don't care, i.e., it doesn't matter if the bit is 0 or 1.                                                                                                                                                                                                             |

| 11,10 | ADD1, ADD0      | These two Channel Address bits are used to select the analog input channel for the next conversion if the Sequencer is not being used. If the Sequencer is being used, these two Channel Address bits are used to select the final channel in a consecutive sequence.                                                                        |

| 9, 8  | Mode1,<br>Mode0 | These two mode bits are used to select the configuation on the four Analog Input Pins. They are used in conjunction with the channel Address bits. On the AD7324 the analog inputs can be configured as either 4 Single Ended Inputs, 2 Fully Differential Inputs, 2 Pseudo Differential inputs or 3 Pseudo Differential Inputs. See Table 9 |

| 7,6   | PM1, PM0        | Power Management Bits. These two bits are used to select different power mode options. Table 10.                                                                                                                                                                                                                                             |

| 5     | Coding          | This bit is used to select the type of output coding the AD7324 will use for the next conversion result. If the                                                                                                                                                                                                                              |

# **Preliminary Technical Data**

|     |           | Coding = 0 then the output coding will be 2s Complement. If Coding = 1, then the output coding will be Straight Binary. When operating in Sequence mode the output coding for each channel will be the value written to the coding bit during the last write to the Control Register.                                                                                                                                                                           |

|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | Ref       | Reference bit. This bit is used to enable or disable the internal reference. If this Ref = 0 then the External Reference will be enabled and used for the next conversion and the internal reference will be disabled. If ref = 1 then the Internal Reference will be used for the next conversion. When operating in Sequence mode the Reference used for each channel will be the value written to the Ref bit during the last write to the Control Register. |

| 3,2 | Seq1/Seq2 | The Sequence 1 and Sequence 2 bits are used to control the operation of the Sequencer. See Table 11.                                                                                                                                                                                                                                                                                                                                                            |

| 1   | ZERO      | A zero must be written to this bit to ensure correct operation of the AD7324.                                                                                                                                                                                                                                                                                                                                                                                   |

Table 9. Analog Input Configuration Selection

| Channe | Channel Address Bits |                            | Mode1 =1, Mode0 = 1      |                           | Mode1 = 1, Mode0 =0 |                            | Mode1 = | 0, Mode0 =1            | Mode1 =0, Mode0 =0 |      |  |

|--------|----------------------|----------------------------|--------------------------|---------------------------|---------------------|----------------------------|---------|------------------------|--------------------|------|--|

|        |                      | 3 Pseudo Differential I/ps |                          | 4 Fully Differential i/ps |                     | 2 Pseudo Differential i/ps |         | Four-Single Ended i/ps |                    |      |  |

|        | ADD1                 | ADD0                       | Vin+ Vin- Vin+ Vin- Vin+ |                           | Vin+                | Vin-                       | Vin+    | Vin-                   |                    |      |  |

|        | 0                    | 0                          | Vin0                     | Vin3                      | Vin0                | Vin1                       | Vin0    | Vin1                   | Vin0               | AGND |  |

|        | 0                    | 1                          | Vin1                     | Vin3                      | Vin0                | Vin1                       | Vin0    | Vin1                   | Vin1               | AGND |  |

|        | 1                    | 0                          | Vin2                     | Vin3                      | Vin2                | Vin3                       | Vin2    | Vin3                   | Vin2               | AGND |  |

|        | 1                    | 1                          | Not                      | Allowed                   | Vin2                | Vin3                       | Vin2    | Vin3                   | Vin3               | AGND |  |

Table 10. Power Mode Selection

| PM1 | PM0 | Description                                                                                                                                                                                                          |

|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 1   | <b>Full Shutdown Mode,</b> In this mode all internal circuitry on the AD7324 is powered down. Information in the Control register is retained when the AD7324 is in Full Shutdown Mode.                              |

| 1   | 0   | Auto Shutdown Mode, The AD7324 will enter Full Shut down at the end of each conversion when the control register is updated. All internal circuitry is powered down in Full Shutdown.                                |

| 0   | 1   | Auto Standby Mode, In this mode all internal circuitry is powered down excluding the internal Reference. The AD7324 will enter Auto Standby Mode at the end of the Conversion after the control register is updated. |

| 0   | 0   | Normal Mode, All internal Circuitry is powered up at all times.                                                                                                                                                      |

Table 11. Sequencer Selection

| Seq1 | Seq2 | Sequence type                                                                                                                                                                                                                                                                                                                                                                                           |

|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0    | The Channel Sequencer is not used. The Analog Channel selected by programming the ADD1 and ADD0 bits in the Control Register selects the next channel for conversion.                                                                                                                                                                                                                                   |

| 0    | 1    | This selects the Sequence of Channels as previously programmed in the Sequence register for conversion. The AD7324 will start converting on the lowest channel in the sequence. It converts the channels in ascending order. If uninterrupted the AD7324 will keep converting the sequence. The range for each channel selected will default to the Ranges previously written into the Range Registers. |

| 1    | 0    | This Configuration is used in conjunction with the Channel Address Bits in the Control Register. It allows continuous conversions on a consecutive sequence of channels, from channel 0, up to and including, a final channel selected by the Channel Address Bits in the control register. The range for each channel will default to the Ranges previously written into the Range Registers.          |

| 1    | 1    | The Channel Sequencer is not used. The Analog Channel selected by programming the ADD1 and ADD0 bits in the Control Register selects the next channel for conversion.                                                                                                                                                                                                                                   |

#### THE SEQUENCE REGISTER

The Sequence Register on the AD7324 is a 4-Bit Write only register. Each of the four Analog input channels has one corresponding bit in the Sequence Register. To select a channel for inclusion in the sequence set the corresponding channel bit to 1 in the Sequence Register.

Table 12. Sequencer Register

MSB LSB Write Vin0 Vin1 Vin2 Vin3 0 0 0 0 0 0 Register Select 1 Register Select 2 0 0

#### **RANGE REGISTER**

The Range register to used to select one Analog input Range per Analog input channel. Range. It is an 8-Bit write only Register, with two dedicated Range bits for each of the Analog Input Channels from Channel 0 to Channel3. There are four Analog input Ranges to choose from,  $\pm 10$ V,  $\pm 5$ V,  $\pm 2.5$ V, 0 to 10V. A write to the Range Register is selected by setting the Write bit to 1 and the Register Select bits to 0, 1. Once the initial write to the Range Register occurs the AD7324 automatically configures the Analog inputs from Channel 0 to Channel 3 to the appropriate range, as indicated by the Range register, each time any one of these analog input channels is selected. The  $\pm 10$ V input Range is selected by default on each analog input channel. See Table 13.

Table 13. Range Register

| MSB   |              |             |       |       |       |       |       |       |       |       |   |   |   |   | LSB |

|-------|--------------|-------------|-------|-------|-------|-------|-------|-------|-------|-------|---|---|---|---|-----|

| Write | Reg Select 1 | Reg Select2 | Vin0A | Vin0B | Vin1A | Vin1B | Vin2A | Vin2B | Vin3A | Vin3B | 0 | 0 | 0 | 0 | 0   |

| VinXA | VinXB | Description                                                           |

|-------|-------|-----------------------------------------------------------------------|

| 0     | 0     | This combination selects the ± 10V<br>Input Range on Analog Input X.  |

| 0     | 1     | This combination selects the ±5V Input Range on Analog Input X.       |

| 1     | 0     | This combination selects the ± 2.5V<br>Input Range on Analog Input X. |

| 1     | 1     | This combination selects the 0 to 10V Input Range on Analog Input X.  |

#### **SEQUENCER OPERATION**

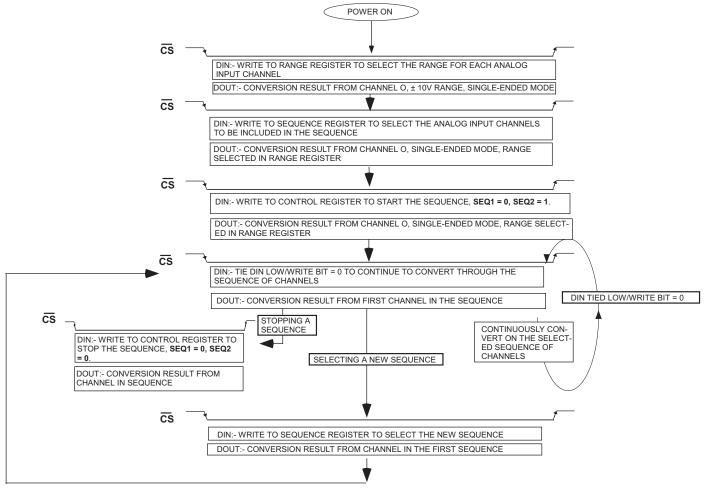

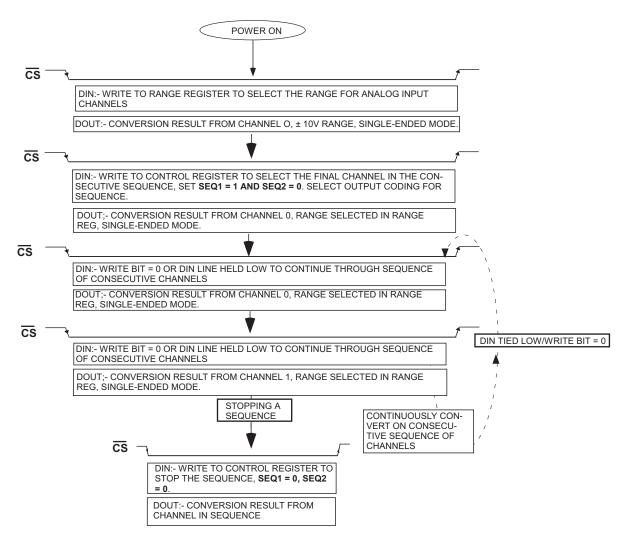

Figure 13. Programmable sequence Flow Chart

The AD7324 can be configured to automatically cycle through a number of selected channels using the on-chip sequence register and the SEQ1 and SEQ2 bits in the control register. Figure 13 shows how to program the AD7324 register in order to operate in sequence mode.

After power up all of the three on-chip registers will contain default values. Each analog input will have a default input range of  $\pm$  10V. If different Analog input ranges are required then a write to the range register is required, this is shown in the first serial transfer in Figure 13. This initial serial transfer is only necessary if Input ranges other than the default Ranges are required. After the Analog Input ranges are configured a write to the Sequence register is necessary to select the channels to be included in the sequence. Once the channels for the sequence have been selected, the sequence can be initiated by writing to the control register and setting the SEQ1 =0, SEQ2 = 1. The AD7324 will continue to convert through the selected sequence uninterrupted provided the Sequence Register remains unchanged and SEQ1 = 0 and SEQ2 = 1 in the Control Register.

If during a sequence a change to one of the range registers is required, it is first necessary to stop the sequence by writing to the Control Register and setting SEQ1=0 and SEQ2=0. Next the write to the range register can be completed to change the required range. Then the previously selected sequence can be initiated again by writing to the Control Register and setting SEQ1=0 and SEQ2=1, the ADC will then convert on the first channel in the sequence.